随着半导体工艺进入纳米尺度,集成电路设计的复杂度显著提升。全芯片分级模拟与分析技术应运而生,成为确保设计成功的关键环节。

在纳米集成电路设计中,全芯片模拟面临巨大挑战。器件尺寸缩小导致量子效应、寄生参数和工艺变异的影响更加显著。传统单层模拟方法难以准确预测芯片性能,而分级模拟通过将整个芯片划分为多个层次——从晶体管级到模块级再到系统级——进行逐层分析与验证,有效解决了这一问题。

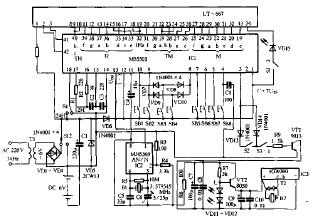

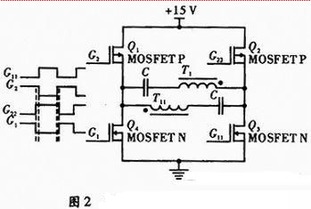

分级模拟的核心优势在于其平衡了精度与效率。在底层,采用SPICE级仿真确保关键路径的精确建模;在中间层,使用硬件描述语言进行功能验证;在顶层,通过行为级模型评估系统性能。这种分层方法大幅减少了仿真时间,同时保持了必要的精度。

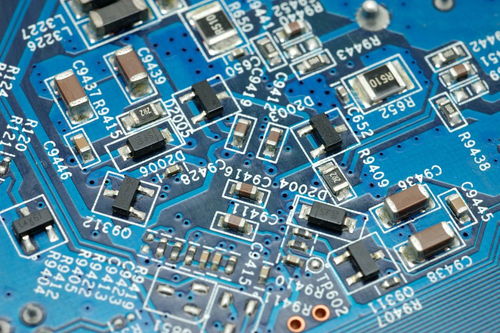

分析环节同样采用分级策略。寄生参数提取分为局部和全局两个层次,时序分析采用静态时序分析与动态仿真相结合,功耗分析则从单元级到芯片级逐步展开。这种分级分析方法能够及早发现问题,避免设计后期昂贵的修改成本。

值得注意的是,分级模拟与分析需要先进的设计自动化工具支持。现代EDA工具提供了完整的分级设计流程,包括层次化网表管理、跨层级时序关联和统一的约束管理,确保各层级之间的一致性。

随着集成电路进一步向3nm及以下工艺发展,全芯片分级模拟与分析技术将继续演进。机器学习辅助的模型降阶、异构集成系统的多物理场协同仿真等新技术,将进一步提升分级模拟的准确性和效率,为纳米集成电路设计提供更强大的支撑。